# CONTRIBUTION A LA CONCEPTION D'UN BANC DE VIEILLISSEMENT DES COMPOSANTS DE PUISSANCE SIC

Présenté par : Aina Tsilavina RAMAMONJISOA

Organisme d'accueil : Laboratoire Ampère

Encadré par : Guy CLERC

# LABORATOIRE AMPÈRE (UMR 5005 DU CNRS)

### Département énergie électrique:

- Électronique de puissance

- Haute tension

- Compatibilité électromagnétique

- Modélisation électromagnétique

- Système de stockage de l'énergie électrique

André Marie Ampère

### CONTEXTE

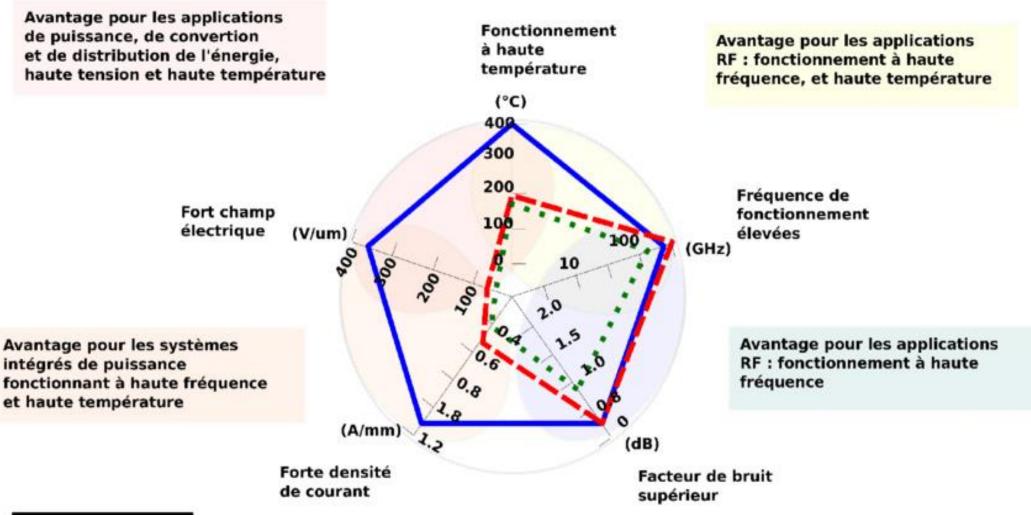

GaN,SiC

GaAs

Si

Source : Tournier, Dominique, Mémoire de thèse - 2012/07/12 - T1 - "Des composants de puissance aux systèmes intégrés haute température en technologie Grand-Gap". DOI - 10.13140/2.1.4325.9680

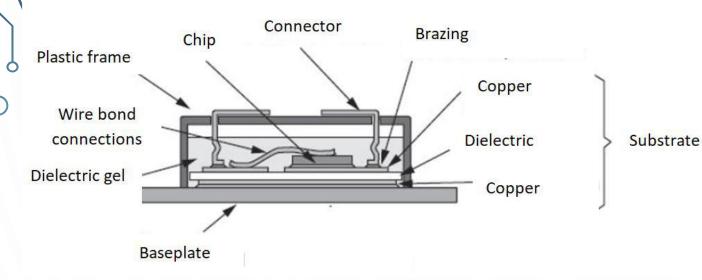

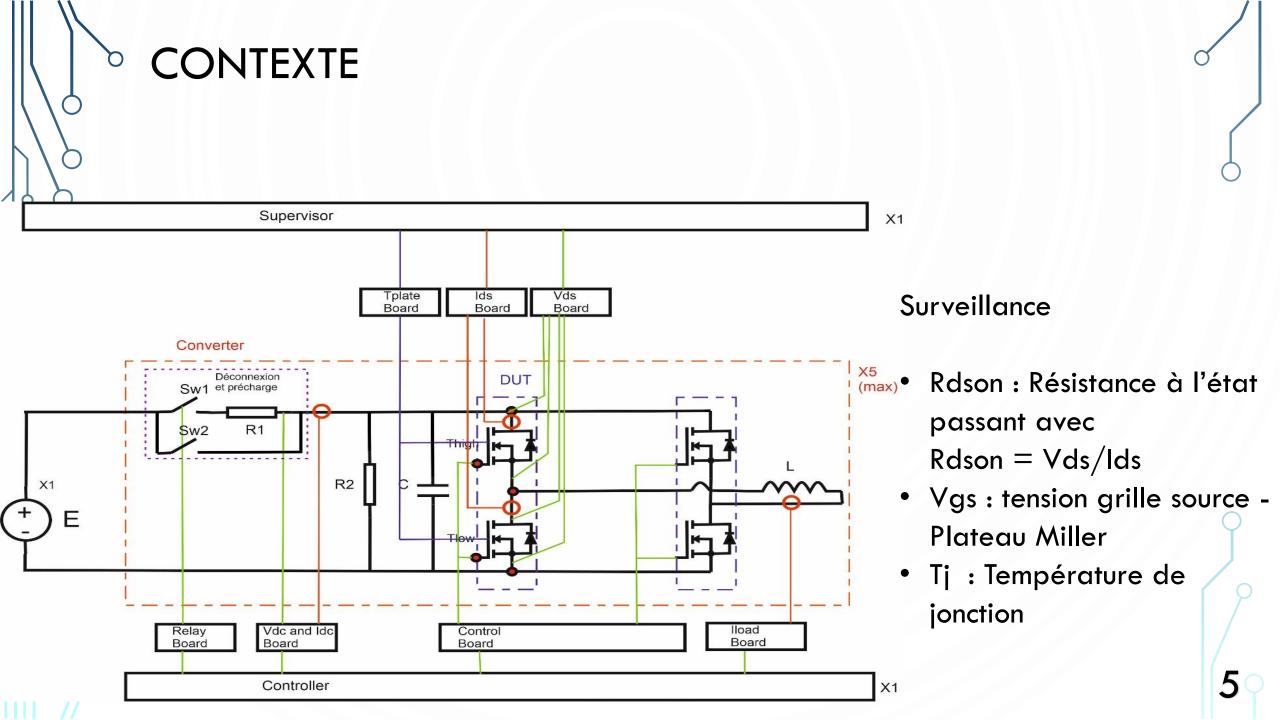

#### CONTEXTE

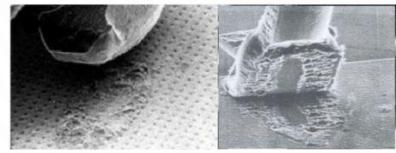

Décollement de fil de bonding.

Source: G. Bower, P. Rogan, J. Kozlowski, and M. Zugger, "SiC power electronics packaging prognostics," in *IEEE Aerospace Conference*, Big Sky, MT, USA, March 2008.

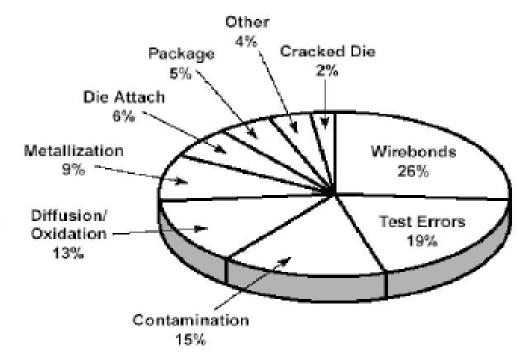

\*Four-year average

Source: Solid State Technology/ ICE, "Readmaps of Packaging Technology"

Modes de défaillance de Mosfet SiC.

Source: G. Bower, P. Rogan, J. Kozlowski, and M. Zugger, "SiC power electronics packaging prognostics," in *IEEE Aerospace Conference*, Big Sky, MT, USA, March 2008.

Le vieillissement reste une inconnue.

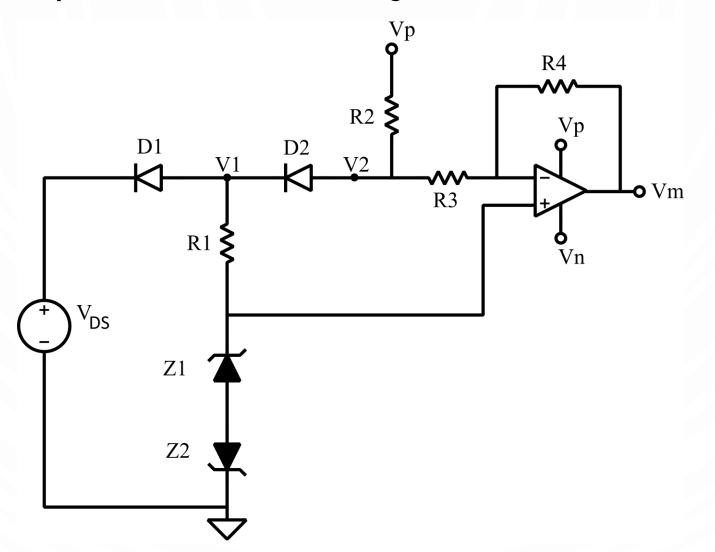

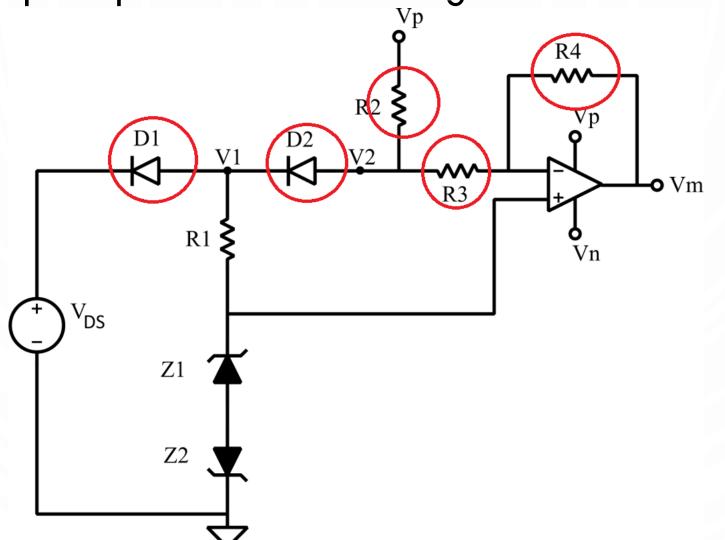

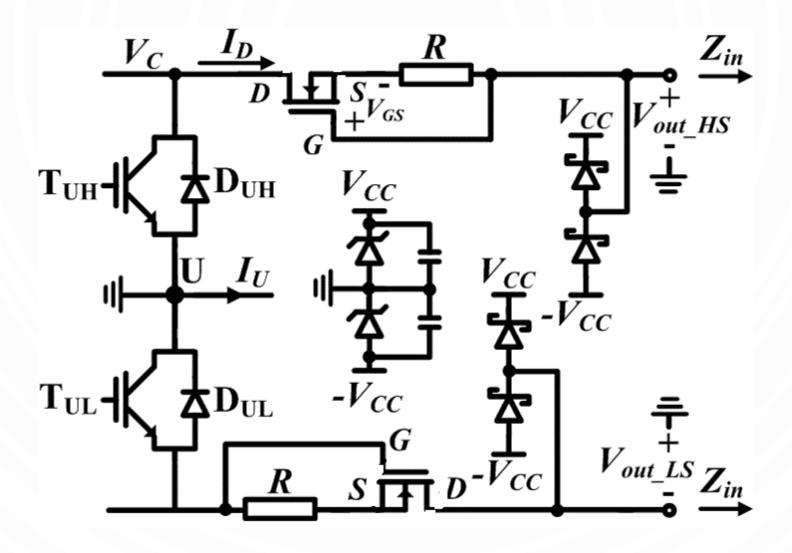

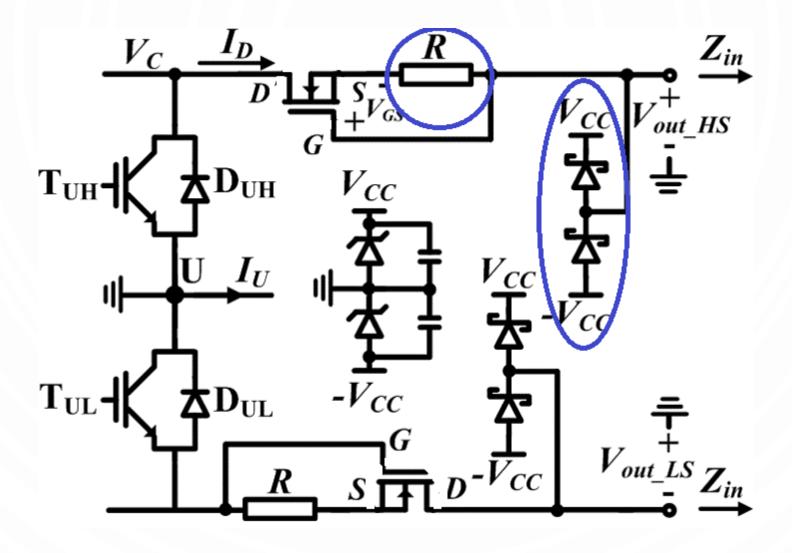

# PREMIER MONTAGE

Proposé par la thèse de Diego Velazco

# PREMIER MONTAGE

Proposé par la thèse de Diego Velazco

# PREMIER MONTAGE

• Proposé par la thèse de Diego Velazco

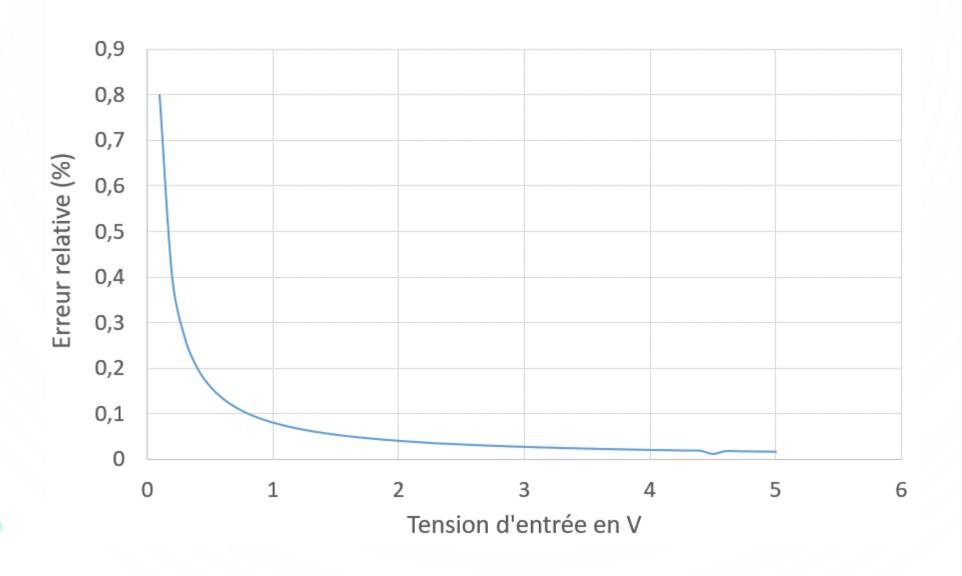

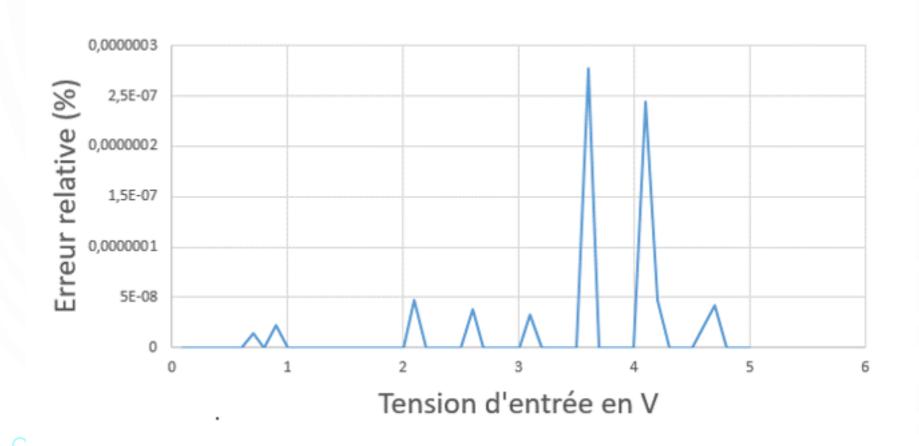

# ÉTUDE DE LA LINÉARITÉ

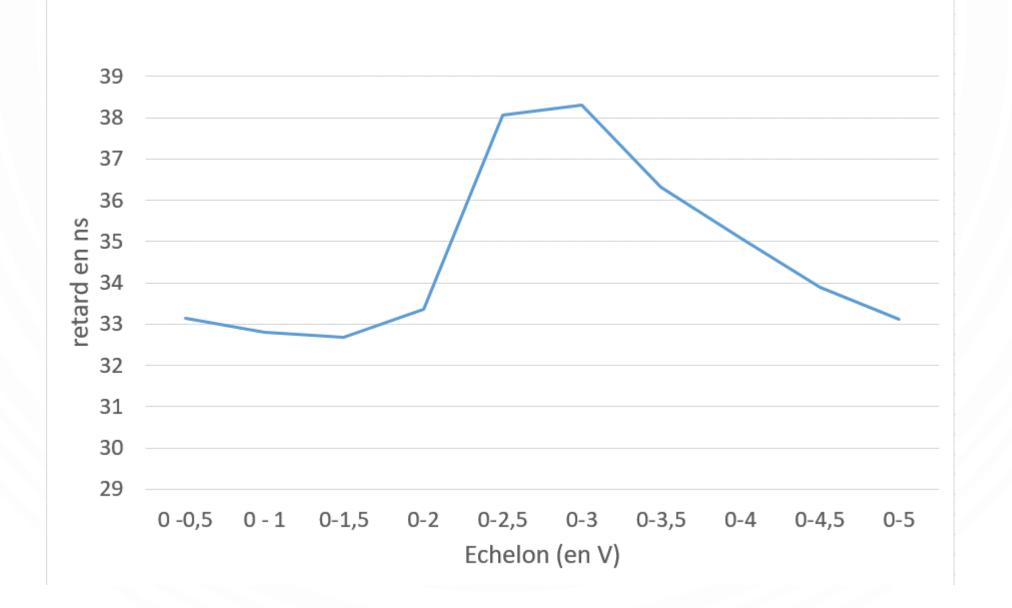

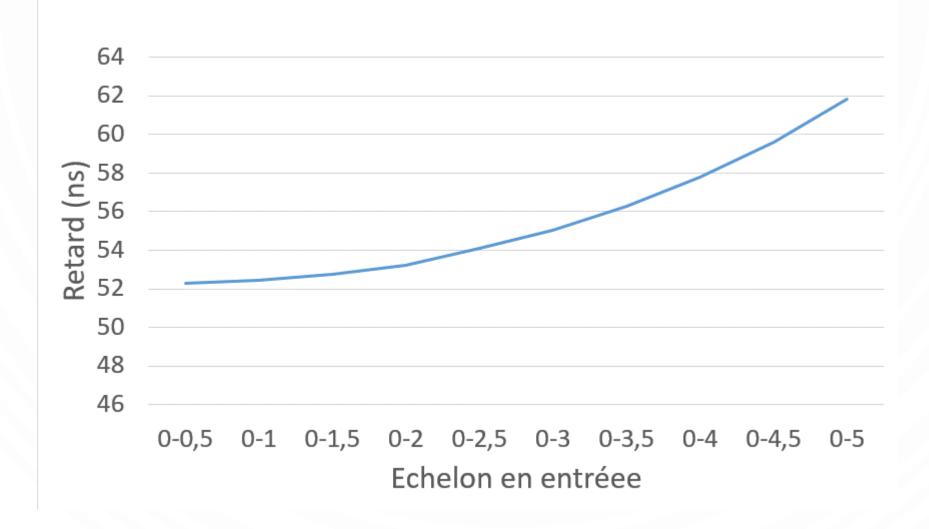

# ÉTUDE DU RETARD

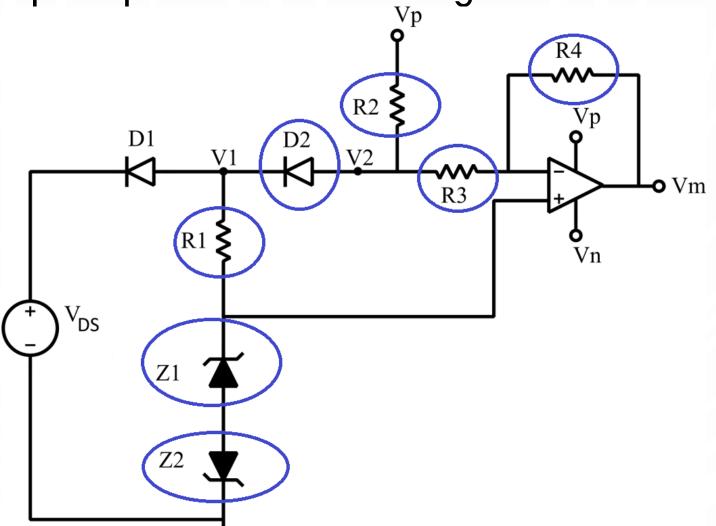

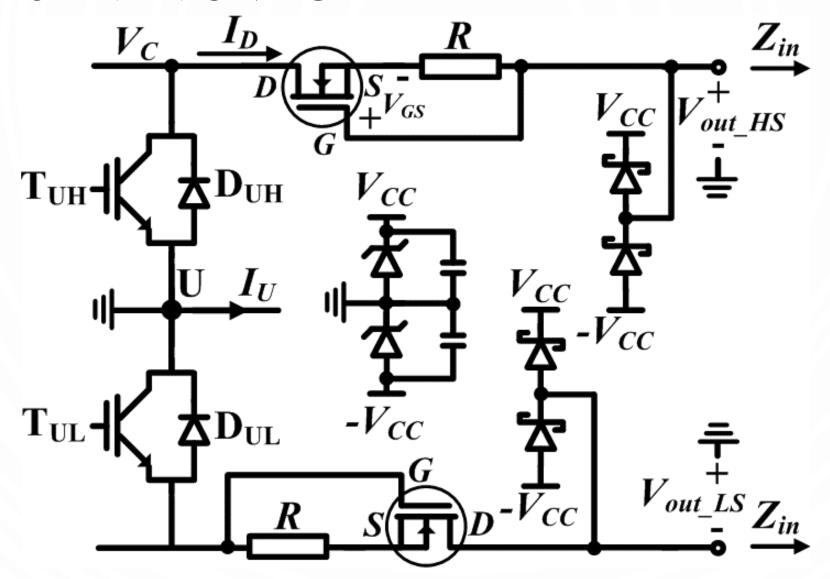

### DEUXIÈME MONTAGE

### DEUXIÈME MONTAGE

### DEUXIÈME MONTAGE

### ÉTUDE DE LA LINÉARITÉ

## ÉTUDE DU RETARD

### CONCLUSION

**Evaluation performance**

•premier montage : erreur relative : 0,01% à 0,1%

retard: <40 ns

•deuxième montage : erreur relative: 0% à  $3.10^{-7}\%$

retard : 52 ns<retard<64ns

#### Perspective

- •Réalisation de la carte électronique

- •Test sur banc de puissance